| Konwersja wewnętrznej izolacji różnicowej |  |

| Rozdzielczość: 16 bitów | |

| Wyjście zatrzasku trójstanowego | |

| Nieprzerwane śledzenie podczas przesyłania danych | |

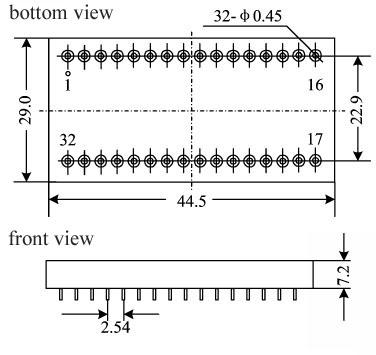

| 32-przewodowy pakiet metalowy |

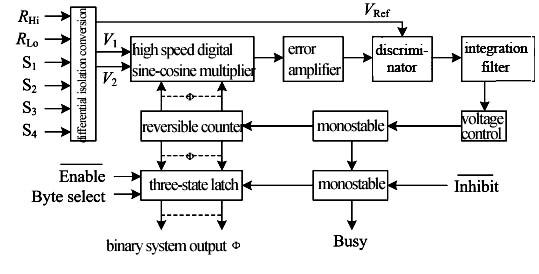

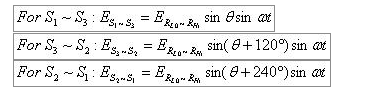

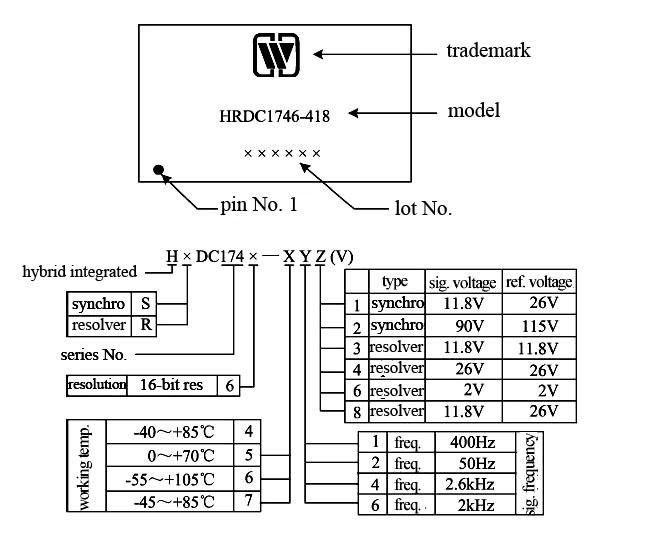

Zaprojektowano synchronizator/resolwer z serii HSDC/HRDC1746 na konwerter cyfrowy | na zasadzie zasady śledzenia serwomechanizmu typu II i przyjmuje | |||||

wejście izolacji różnicowej, wyjście danych przyjmuje zatrzask trójstanowy; | tryb, nadaje się do konwersji sygnału analogowego/sygnału cyfrowego | trójprzewodowy synchronizator i czteroprzewodowy przelicznik. Z dużą szybkością konwersji | oraz stabilna i niezawodna wydajność, to urządzenie może być szeroko stosowane; w pomiarze kąta i automatycznym systemie sterowania. | Ten produkt jest wytwarzany w grubowarstwowym hybrydowym procesie integracji i jest | ||

Całkowicie uszczelniona metalowa obudowa z 32-przewodami DIP. Zarówno projekt, jak i | ||||||

produkcja wyrobu spełnia wymagania GJB2438A-2002 | „Ogólna specyfikacja hybrydowych układów scalonych” i specyficzna | specyfikacje produktu. | ||||

4. Parametry elektryczne (tabela 2, tabela 3) | Konwertery synchronizujące na cyfrowe lub konwertery resolwerowe na cyfrowe (seria HSDC/HRDC1746) | Tabela 2 Warunki znamionowe i zalecane warunki pracy | Tabela 3 „Charakterystyka elektryczna” | Maks. bezwzględna Wartość znamionowa | ||

Napięcie zasilania Vs: ± 17,25VDC | Parametr | -3 | 3 | |||

HSDC/HRDC | Seria 1746 | 16 | ||||

Uwagi | Logiczne napięcie zasilania VL: +7V | 50 | Zakres temperatury przechowywania: -55 ℃ ~ 150 ℃ | |||

Min. | Maks. | 2 | 90 | |||

Zalecane warunki pracy | Napięcie zasilania Vs: ±15±5% | 2 | Dokładność/minuta kątowa | |||

| 2,6 tys |  |

| Przesunięcie fazowe między sygnałem a wzbudzeniem: <±10% Napięcie sygnału (wartość skuteczna)/V Zakres temperatury roboczej (TA): -40~+105℃  | |

| Napięcie odniesienia (wartość skuteczna)/V | 115 |

| |

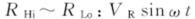

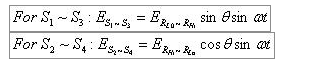

| otrzymujemy funkcję błędu: |

Poprzez wzmocnienie błędu, dyskryminację fazową i filtrację tegoof funkcję błędu sin(θ-φ) otrzymujemy, gdy θ-φu003d0 (w zakresie dokładności | konwertera), ten błąd spowoduje, że napięcie będzie kontrolowaneofimpuls korekcji wyjścia oscylatora do zmiany binarnego kąta cyfrowego φ |

| |

| licznika rewersyjnego tak, aby wartość wyjścia φ była równa | wejście θ w zakresie dokładności konwertera, system staje się stabilny |

| i może śledzić zmianę kąta wejściowego φ. W ten sposób binarny cyfrowy | |

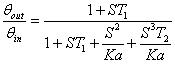

licznik odwracalny (rys. 2). | Rys. 2 Schemat blokowy obwodu | (1) Charakterystyka dynamiczna | Funkcja przenoszenia konwertera jest pokazana na rys. 3: | Wzmocnienie w pętli otwartej: | Funkcja zamkniętej pętli: |

1 | NC | Dla modułu tego modelu Kau003d48000/S2, T1u003d7,1ms, T2u003d1,25ms | 17 | NC | Rys. 3 Przenoszenie funkcji konwertera |

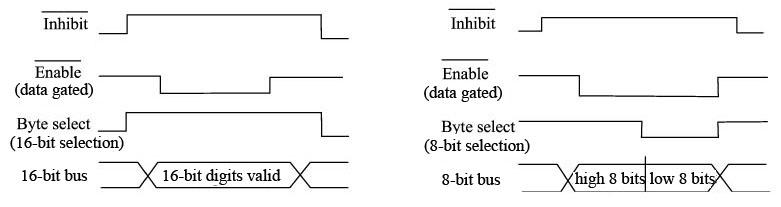

2 | D9 | (2) Metody przesyłania danych i sekwencja czasowa | 18 | Włącz kontrolę wyboru chipa | Ten pin jest pinem wejściowym logiki sterującej, jego funkcją jest wyjście; |

3 | dane do konwertera w celu realizacji sterowania trójstanowego. Niski poziom to | prawidłowe, dane wyjściowe konwertera zajmują magistralę danych. Kiedy jest o godz | 19 | wysoki poziom, pin wyjściowy danych konwertera znajduje się w trzech stanach, the | urządzenie nie zajmuje magistrali. |

4 | Wybór bajtów | Ten pin jest pinem wejściowym sterującym, jego funkcją jest wykonanie zewnętrzne; | 20 | kontrola wyboru na danych wyjściowych konwertera w transmisji | tryb 8-bitowej magistrali danych lub 16-bitowej magistrali danych. W przypadku 16-bitowego transferu magistrali danych |

5 | tryb jest wymagany, trzymaj ten pin logiczny wysoko, dane będą | przesyłane w magistrali, wyjście starszego bajtu znajduje się na stykach D1 do D8 (D1 jest | 21 | wysoki bit) i niski bajt znajdują się w D9 do D16. W przypadku transferu 8-bitowej magistrali danych | potrzebny jest tryb, dane pobierane są w pinach D1 do D8 (ułożone od wysokiego |

6 | do niskiego), a wysokie 8 bitów i niskie 8 bitów uzyskuje się przez dwa razy | sekwencje, innymi słowy, gdy wybór bajtu ma wartość logiczną wysoką, wysoką 8 bitów | 22 | są wyprowadzane, a gdy jest to stan logiczny niski, wyprowadzanych jest 8 bitów o niskim stanie. | Kontrola blokowania danych (sygnał wstrzymujący) Wstrzymanie |

7 | Ten pin jest pinem wejściowym logiki sterującej, jego funkcją jest wyjście; | dane zewnętrznie do konwertera w celu realizacji opcjonalnego zatrzasku lub obejścia; | 23 | kontrola. Na wysokim poziomie dane wyjściowe konwertera są bezpośrednio | wyjście bez zatrzasku, patrz diagram sekwencji czasowej danych |

8 | przenosić. Na niskim poziomie dane wyjściowe konwertera są zatrzaskiwane, | pętla wewnętrzna nie jest przerywana, a śledzenie działa przez cały czas | 24 | D1 | czas, ale licznik nie wyświetla danych. Kiedy jest to potrzebne do przeniesienia |

9 | danych, konwerter najpierw wysyła sygnał sterujący Inhibit, aby zablokować dane od wysokiego do niskiego, utrzymuje stan logiczny na niskim poziomie przez 640 ns, następnie ustawia wejście Enable na niski (w tym czasie urządzenie zajmuje szynę danych), a następnie | uzyskuje dane poprzez wybór bajtów, a następnie ustawia wszystkie logikę sterowania na wysoki | 25 | D2 | odświeżyć i zablokować dane, aby przygotować się do przeniesienia |

10 | kolejne dane, proszę odnieść się do wykresów sekwencji czasowych przesyłania danych Rys.4 | i Rys.5. | 26 | D3 | (3)Metoda tłumienia sygnału wejściowego (rys.4 i rys.5) |

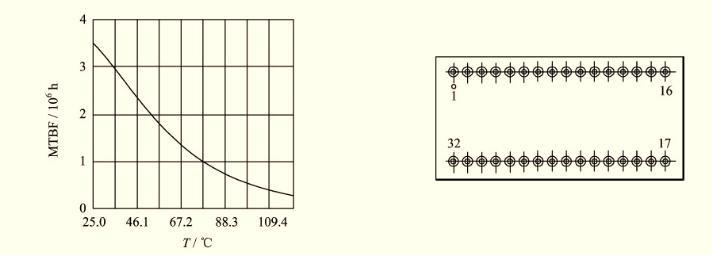

11 | Rys. 4 Sekwencja czasowa 16-bitowego transferu magistrali | Ryc.5 Sekwencja czasowa 8-bitowego transferu magistrali | 27 | D4 | 6. Krzywa MTBF (rys. 6) |

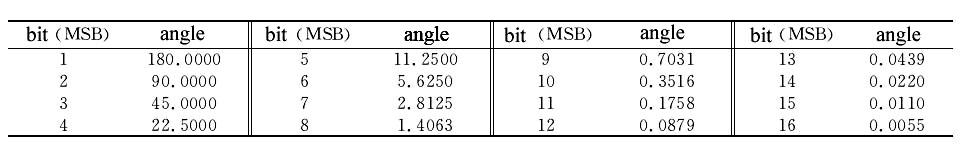

12 | Konwertery synchronizujące na cyfrowe lub konwertery resolwerowe na cyfrowe (seria HSDC/HRDC1746) | 7. Oznaczenie pinów (rys.7, tabela 4) | 28 | D5 | Konwertery synchronizujące na cyfrowe lub konwertery resolwerowe na cyfrowe (seria HSDC/HRDC1746) |

13 | S3 | Rys.6 Krzywa MTBF-temperatura | 29 | D6 | Rys.7 Oznaczenie pinów (widok od dołu) |

14 | S2 | (Uwaga: zgodnie z GJB/Z299B-98, przewidywany dobry stan podłoża) | 30 | D7 | Tabela 4 Opis funkcjonalny zacisków przewodów |

15 | S1 | Szpilka | 31 | D7 | Symbol |

16 | NC | Oznaczający | 32 | NC | Szpilka |

Grunt | D12 | Wyjście cyfrowe dla 12 bitów | -VS | -15V zasilanie | D13 | Wyjście cyfrowe dla 13-bitowego | + VS | Zasilanie +15V |

D14 | Wyjście cyfrowe dla 14-bitowego | Ni | Hamować | Ni | Kontrola blokowania danych | D15 | Wyjście cyfrowe dla 15 bitów |

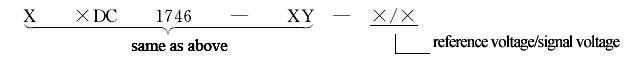

X

X