| Wysoka celność |  |

| Mały rozmiar | |

| Wysoka prędkość śledzenia | |

| Nieprzerwane śledzenie podczas przesyłania danych | |

| Wyjście zatrzasku trójstanowego | |

| Niski pobór mocy |

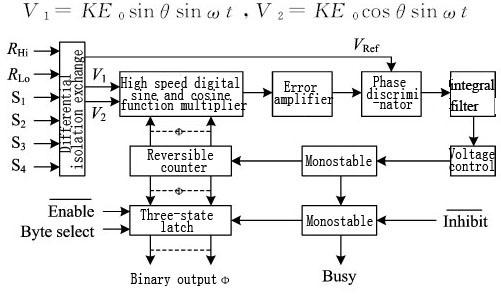

sygnał wyjściowy jest równoległym naturalnym kodem binarnym buforowanym przez | zatrzask trzystanowy i kompatybilny z poziomem TTL. |

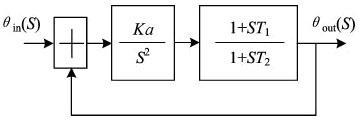

Produkt stosuje obwód serwo drugiego rzędu o niewielkich rozmiarach i świetle | |

waga, a użytkownik może bardzo wygodnie z niej korzystać, kontrolując | |

piny sygnałowe. | |

Tabela 2 Warunki znamionowe i zalecane warunki pracy | Maks. bezwzględna wartość oceny |

Napięcie zasilania +VS: 12,5~17,5V | |

Napięcie zasilania -VS: -17,5~-12,5V | |

Napięcie logiczne VL: 7V | |

Zakres temperatury przechowywania: -40 ~ + 100 ℃ | |

Zalecane warunki pracy |

Napięcie odniesienia (wartość skuteczna) VRef: wartość nominalna ±10% | Napięcie sygnału (wartość skuteczna) V1*: wartość nominalna ±10% Częstotliwość odniesienia f*: wartość nominalna ±10% | Zakres temperatury pracy TA: -40~+85℃ | Uwaga: * oznacza, że można go dostosować zgodnie z wymaganiami użytkownika. | |

Tabela 2 „Charakterystyka elektryczna” | Parametr | |||

Warunki (-40~+85 ℃) | (O ile nie podano inaczej) | 12 | 16 | (seria MSDC/MRDC37) |

Jednostka | – | 3 | 36 | Min. |

Maks. | Rozdzielczość/OZE | Zakres 0~360º | – | V |

Fragment | Prędkość śledzenia/St① | – | rps | V |

Wysoki poziom wyjściowy/VOH | TA u003d 25 ℃ | – | 2,4 | W |

Niski poziom wyjściowy/VOL | TA u003d 25 ℃ | – | 0,8 | % |

Pobór mocy/PD | – | 2 | TA u003d 25 ℃ | V |

1,3 | – | 2 | 90 | V |

Liniowość Vel/ERl | – | 30 | TA u003d 25 ℃ | Hz |

1,0 | – | ±3 | Zakres napięcia odniesienia | 115 |

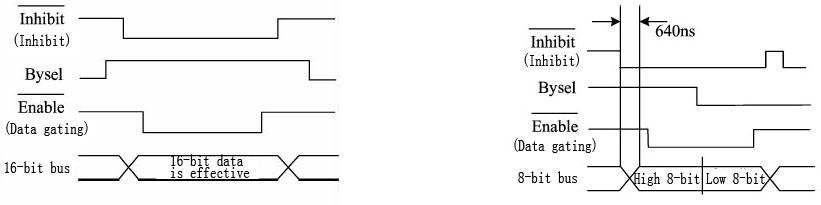

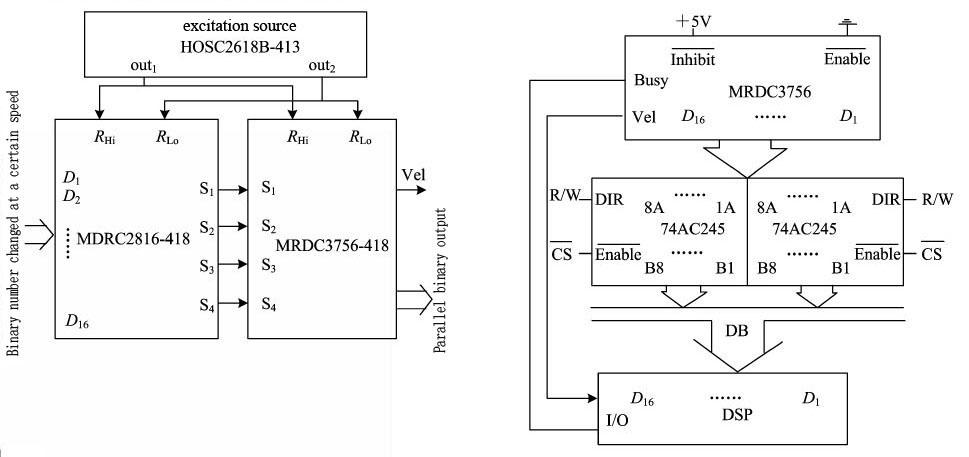

B: konwerter jest podłączony do szyny 8-bitowej, bity D1~D8 są podłączone do szyny danych, a reszta jest pusta. | Ustaw wstrzymanie z logicznego 1 na logiczne 0 (blokada danych) i odczekaj 1 μs; ustaw Enable na logiczne 0, aby umożliwić zatrzaskowi w konwerterze dane wyjściowe; ustawić | Bysel do logiki 1, bezpośrednio odczytaj wysokie 8-bitowe dane, ustaw Bysel na | logiczne 0, odczytaj dane w innych bitach z automatycznym wypełnianiem zerami w | puste bity; ustawić na logiczny 1, aby przygotować się do odczytu kolejnych skutecznych danych (rys. 5). | Hamować | Rys4 Sekwencja czasowa 16-bitowego transferu magistrali | (2) Zajęta metoda (odczyt asynchroniczny): | W trybie odczytu asynchronicznego opcja Wstrzymanie jest ustawiona na wartość logiczną 1 lub jest pusta, niezależnie od tego, czy pętla wewnętrzna jest zawsze w |

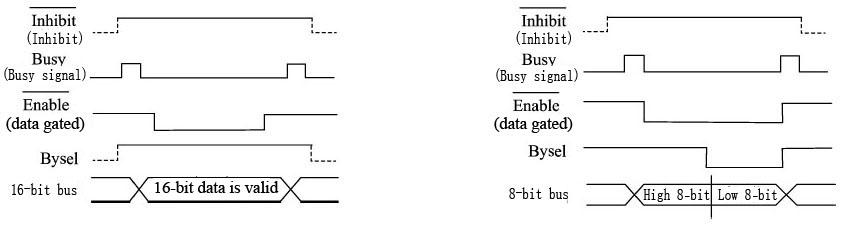

1 | D1 | należy określić stan stabilny lub czy dane wyjściowe są prawidłowe | 13 | poprzez stan sygnału zajętości Busy. Gdy sygnał zajętości jest wysoki | poziomie, wskazuje, że dane są konwertowane, a dane na tym poziomie | 25 | czas jest niestabilny i nieważny; gdy sygnał zajętości jest niski, to | wskazuje, że konwersja danych została zakończona, a dane w tym momencie |

2 | D2 | czas jest stabilny i ważny. Gdy podczas czytania pojawi się wysoki poziom w trybie zajęty, | 14 | odczyt w tej chwili jest nieważny. W trybie odczytu asynchronicznego | Zajęte wyjście to ciąg impulsów na poziomie TTL, jego szerokość zależy od jego | 26 | prędkość obrotowa, istnieją również dwa sposoby wykorzystania magistrali tj. 8-bitowa | i 16-bitowy, odczyt danych podczas efektywnego wyprowadzania danych jest również |

3 | D3 | kontrolowane przez Enable , proszę odnieść się do diagramu sekwencji czasowej dla transferu danych (rys. 6 i rys. 7). | 15 | Ryc.6 Wykres sekwencji czasowej dla 16-bitowego transferu magistrali Ryc.7 Diagram sekwencji czasowej dla 8-bitowego transferu magistrali | Piny sygnału statusu: zajęty, DIR, R, C. | 27 | Gdy zmienia się wejście konwertera, Busy wyprowadza ciąg impulsów | poziomu CMOS, jego częstotliwość jest określana przez najwyższą rotację |

4 | D4 | prędkość. Kiedy Busy jest na wysokim poziomie, oznacza to, że serwomechanizm drugiego rzędu | 16 | obwód w konwerterze działa, dane na końcu wyjścia cyfrowego są | wymiana pieniędzy; wręcz przeciwnie, komputer może bezpośrednio odczytywać dane. | 28 | Sygnał DIR służy do wskazywania obrotów do przodu/do tyłu. Kiedy wyjście | |

5 | D5 | kod jest zliczany, wyjście jest na wysokim poziomie; gdy kod wyjściowy to | 17 | NC | odliczanie w dół, wyjście ma niski poziom. | 29 | Wyjście sygnału zerowego R.C: gdy dane wyjściowe wzrastają od wszystkich 1 do | wszystkie 0 lub dane wyjściowe zmniejszają się ze wszystkich 0 do wszystkich 1, |

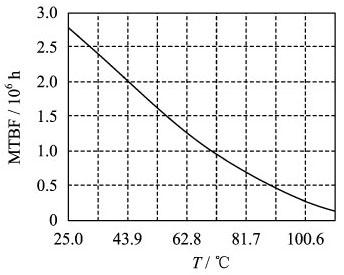

6 | D6 | wyjście jest impulsem dodatnim, szerokość impulsu wynosi 200 μs. | 18 | 5. Krzywa MTBF przetworników Synchro-Digital lub Resolver-Digital (seria MSDC/MRDC37) (rys. 7) | Ryc. 8 Krzywa MTBF-temperatura | 30 | (Uwaga: zgodnie z GJB/Z299B-98, przewidywany dobry stan podłoża) | |

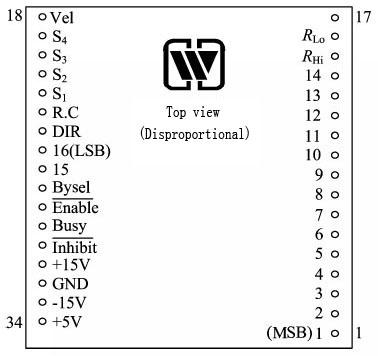

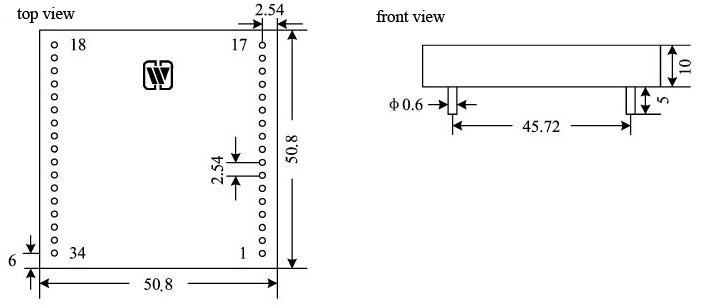

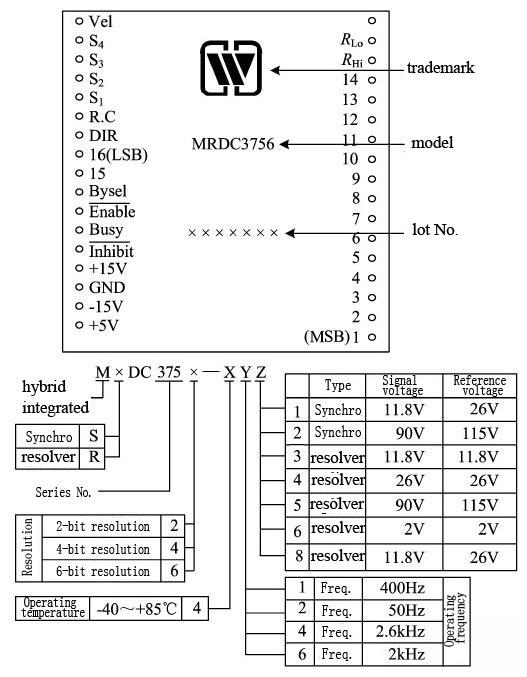

7 | D7 | 6. Oznaczenie pinów konwerterów Synchro na cyfrowe lub resolwera na konwertery cyfrowe (seria MSDC/MRDC37) (rys. 9, tabela 3) | 19 | S4 | Rys. 9 Oznaczenie styków (widok z góry) | 31 | Tabela 3 „Oznaczenie pinów” | Szpilka |

8 | D8 | Symbol | 20 | S3 | Oznaczający | 32 | Szpilka | Symbol |

9 | D9 | Oznaczający | 21 | S2 | Szpilka | 33 | Symbol | Oznaczający |

10 | Wyjście cyfrowe 1 (najwyższy bit) | D13 | 22 | S1 | Wyjście cyfrowe 13 | 34 | VL | D16 |

11 | Wyjście cyfrowe 16 | Wyjście cyfrowe 2 | 23 | D14 | Wyjście cyfrowe 14 | |||

12 | D15 | Wyjście cyfrowe 15 | 24 | Wyjście cyfrowe 3 | RHi |

Wejście sygnału odniesienia (dolny koniec) | Włącz sygnał | Wyjście cyfrowe 5 | Ślepy zaułek | Zajęty | Zajęty sygnał |

Wyjście cyfrowe 6 | Vel | 7 | Wyjście napięciowe prędkości | 13 | Zablokuj sygnał |

2 | Wyjście cyfrowe 7 | 8 | Wejście sygnału | 14 | +Vs |

3 | Zasilanie +15 V | 9 | Wyjście cyfrowe 8 | 15 | Wejście sygnału |

4 | GND | 10 | Uziemienie zasilania | 16 | Wyjście cyfrowe 9 |

5 | Wejście sygnału | 11 | -Vs | ||

6 | -15 V zasilanie | 12 | D10 |

| |

| Wejście sygnału | Zasilanie +5 V |

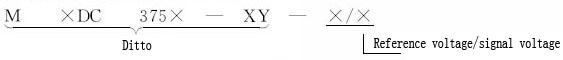

X

X