Moc robocza przyjmuje zasilanie ±15 V i + 5 V DC. Istnieją dwa rodzaje sygnału wyjściowego: trzyliniowy sygnał synchronizujący i referencyjny (konwerter SDC) lub czteroliniowy przelicznik i sygnał odniesienia (konwerter RDC); wyjście przyjmuje równoległe kody cyfrowe systemu binarnego.

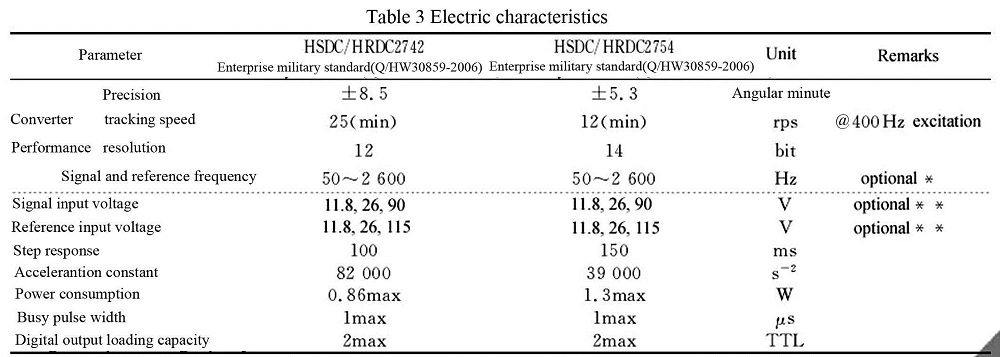

| Rozdzielczość: 12 bitów, 14 bitów |  |

| Wysoka prędkość śledzenia | |

| Integracja hybrydowa, metalowa obudowa | |

| Wyjście zatrzasku trójstanowego | |

| Z wyjściem sygnału prędkości Vel | |

| Nieograniczona kompatybilność z serią AD1740 |

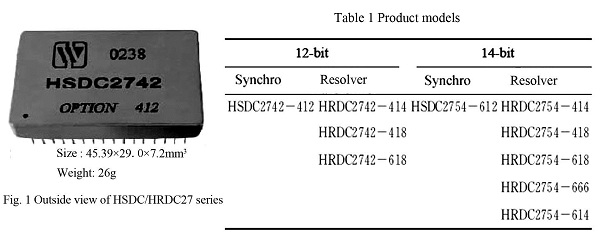

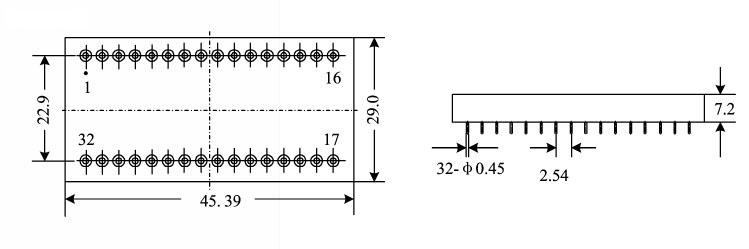

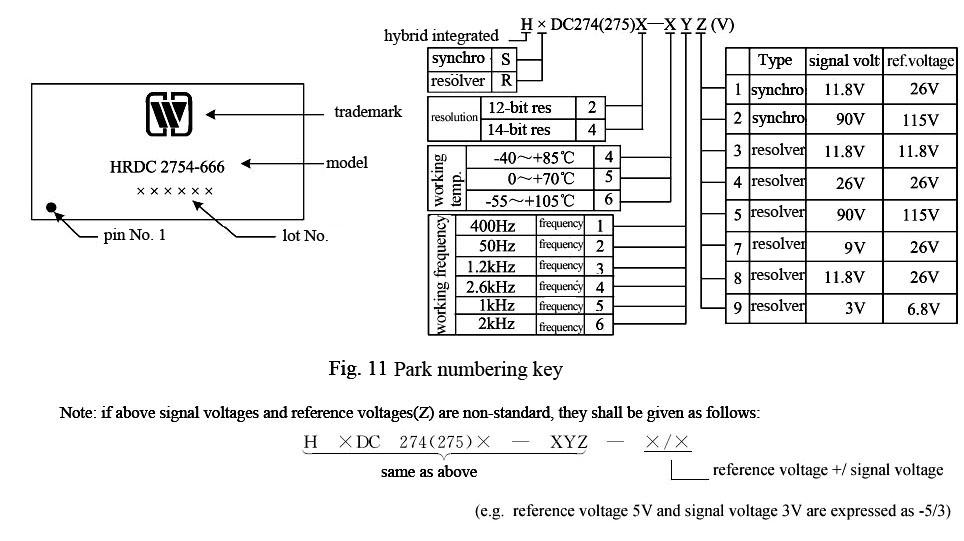

Seria HSDC/HRDC27 to konwertery cyfrowo-synchro lub konwertery resolwera na cyfrowe do ciągłego śledzenia pętli serwo typu II, równolegle zatrzaskują i wyprowadzają 12-bitowe lub 14-bitowe naturalne dane zakodowane binarnie z 32-liniowym metalem dual-in-line pakiet, ma zalety małej objętości, lekkości i wysokiej niezawodności itp., jest szeroko stosowany w takich automatycznych systemach sterowania, jak system radarowy, system nawigacyjny itp.

Moc robocza przyjmuje zasilanie ±15 V i + 5 V DC. Istnieją dwa rodzaje sygnału wyjściowego: trzyliniowy sygnał synchronizujący i referencyjny (konwerter SDC) lub czteroliniowy przelicznik i sygnał odniesienia (konwerter RDC); wyjście przyjmuje równoległe kody cyfrowe systemu binarnego.

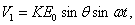

Tabela 2 Ocenione i zalecane warunki pracy

Maks. bezwzględna Wartość znamionowa | Napięcie zasilania Vs: ± 17,5 V |

Napięcie logiczne VL: +5,5 V | |

Zakres temperatur przechowywania: -55 ℃~+125 ℃ | |

Zalecane warunki pracy | Napięcie zasilania Vs: ± 5 V |

Napięcie logiczne VL: 5 V | |

Efektywna wartość napięcia odniesienia VRef: ±10% wartości nominalnej | |

Ważność napięcia sygnału V1*: ± 5% wartości nominalnej | |

Częstotliwość odniesienia f*: 50Hz~2,6kHz | |

Zakres temperatury pracy TA: -40~+85℃,-55~+105℃ |

Uwaga: * wskazuje, że można go dostosować do wymagań użytkownika.

| wyjście; odczyt danych 12-bitowych lub 14-bitowych; ustawić blokadę na logiczne „1”, aby |  |

| 16-bitowy transfer). | B: konwerter jest podłączony do szyny 8-bitowej, bity D1~D8 są podłączone do szyny danych, a reszta jest pusta. |

| |

| Zahamować jest | |

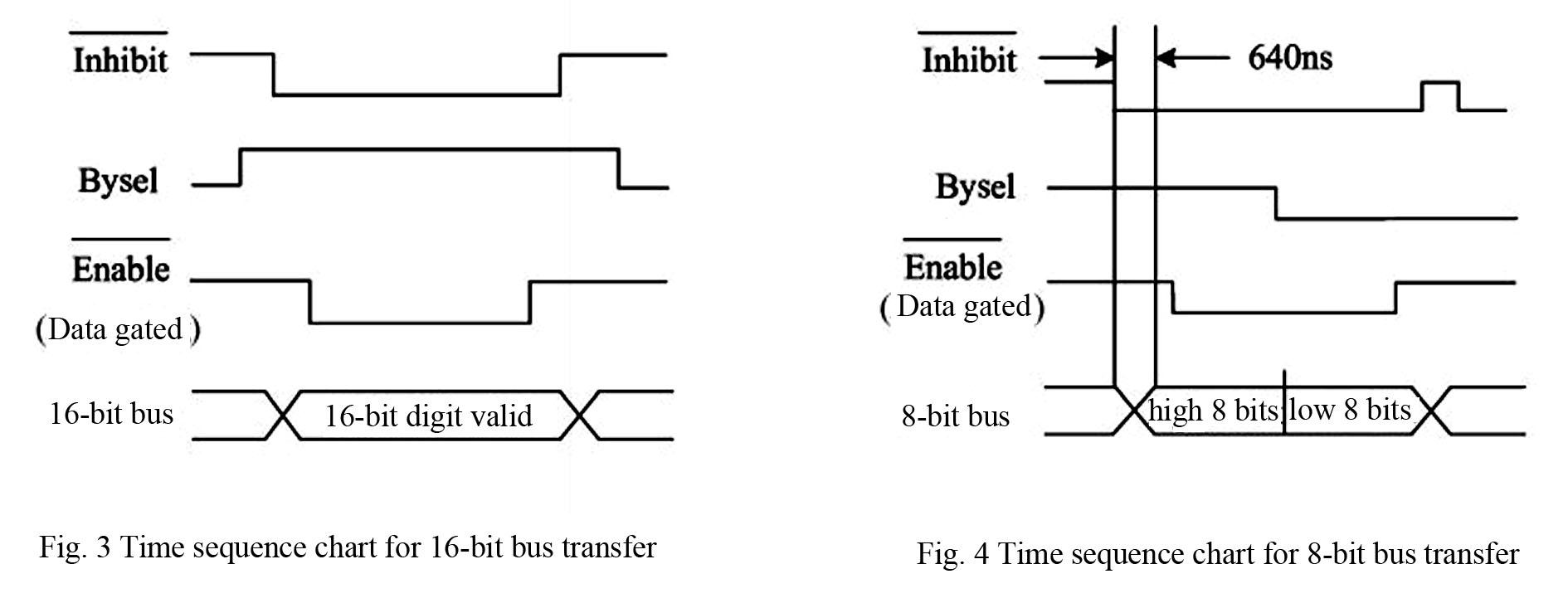

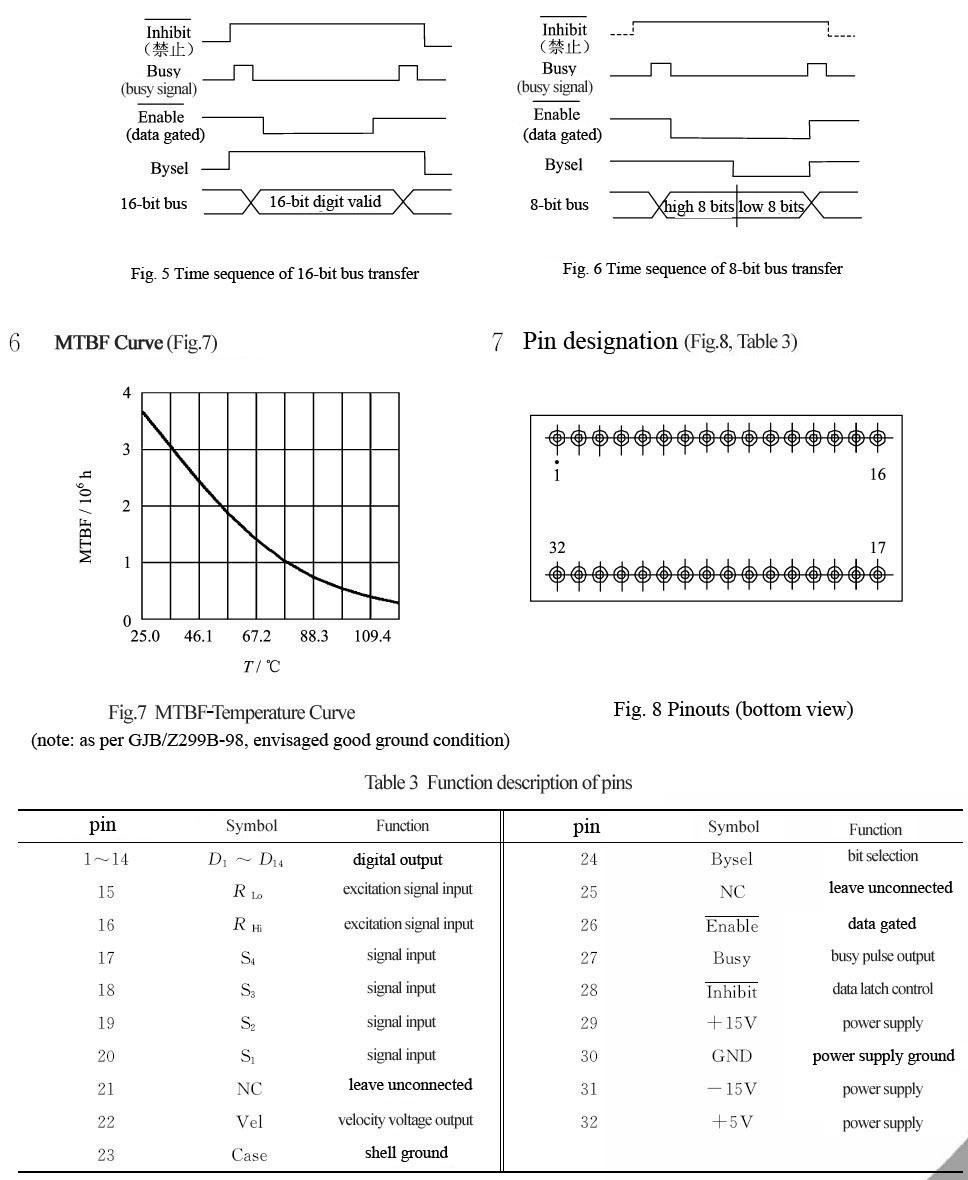

| Włącz logiczne „0”, dane zatrzasku wewnątrz konwertera mogą | być wyjściem; jeśli Byse1 jest ustawione na logiczne „1”, konwerter odczytuje bezpośrednio | wyższe dane 8-bitowe, jeśli Byse1 jest ustawione na logiczne „0”, konwerter odczytuje | pozostałe bity, automatycznie dodaje zero dla niekompletnych bitów; ustaw blokadę blokowania danych wstrzymujących (sygnał wstrzymujący) na logiczne „1”, aby przygotować się do odczytu następnych poprawnych danych (patrz Rys. 3 i Rys. 4 dla 8-bitowej sekwencji czasu transferu) | (2) Zajęta metoda (odczyt asynchroniczny): | W trybie odczytu asynchronicznego sterowanie blokowaniem danych blokowania (sygnał blokujący) jest ustawione na logiczne „1” lub puste, niezależnie od tego, czy pętla wewnętrzna jest zawsze w trybie | należy określić stan stabilny lub czy dane wyjściowe są prawidłowe | przez stan sygnału zajętości Busy. Gdy sygnał zajętości jest wysoki | poziomie, wskazuje, że dane są konwertowane, a dane na tym poziomie |

| czas jest niestabilny i nieważny; gdy sygnał zajętości jest niski, to | wskazuje, że konwersja danych została zakończona, a dane w tym momencie | Au | czas jest stabilny i ważny. Gdy podczas czytania pojawi się wysoki poziom w trybie zajęty, | Au | odczyt tego czasu jest nieważny. W trybie odczytu asynchronicznego, Zajęty | Au | wyjście to ciąg impulsów na poziomie TTL, szerokość między jest związana z | prędkość obrotowa. Podobnie, istnieją również dwa zastosowania 8-bitowe i 16-bitowe |

X

X