| Konwersja wewnętrznej izolacji różnicowej |  |

| Rozdzielczość 16-bitowa | |

| Dokładność: 2 minuty kątowe | |

| Wyjście zatrzasku trójstanowego | |

| Wysoka prędkość ciągłego śledzenia | |

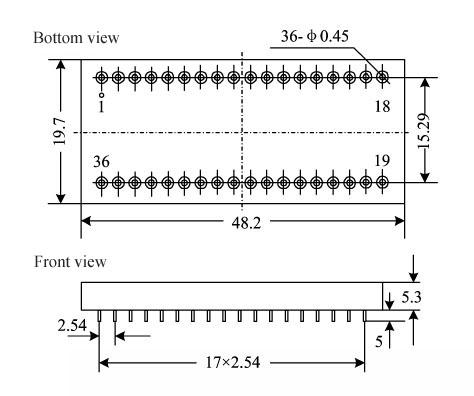

| 36-przewodowy, odporny na mgłę solną, metalowy, uszczelniony pakiet DDIP | |

| Pin-to-Pin zgodny z modelem SDC14560 firmy DDC |

| zintegrowane urządzenie do konwersji do ciągłego śledzenia zaprojektowane na | zasada serwa modelu II. Produkty z tej serii są zaprojektowane i |

| wyprodukowane w procesie MCM, podstawowe elementy przyjmują specjalny układ scalony | |

| opracowany samodzielnie przez nasz instytut. Układ pinów to | |

| kompatybilny z produktami serii SDC14560 amerykańskiej firmy DDC, 16-bitowy | |

| równoległe wyjście z blokadą danych w naturalnym kodzie binarnym, 36-liniowy DIP całkowicie | |

| zamknięte opakowanie metalowe, ma zalety wysokiej precyzji, małe | |

| objętość, niskie zużycie energii, niewielka waga i wysoka niezawodność itp., | i może być szeroko stosowany w ważnej broni strategicznej i taktycznej, takiej jak: |

| samolot, okręt wojenny, armata, pocisk, radar, czołg itp. | |

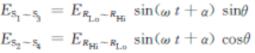

| 4. Wydajność elektryczna (tabela 1, tabela 2) | |

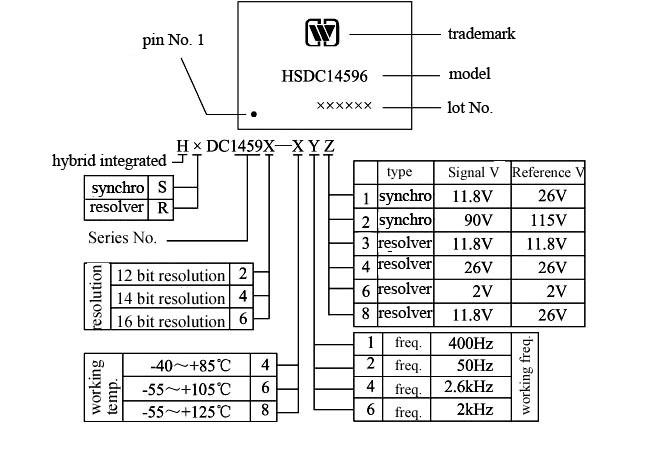

| Przetworniki synchroniczne na cyfrowe lub konwertery resolwerowe na cyfrowe (seria HSDC/HRDC1459) | |

| Tabela 1 Warunki znamionowe i zalecane warunki pracy | |

| Maks. bezwzględna Wartość znamionowa |

| Napięcie sygnału V1: wartość znamionowa ±20% | Napięcie odniesienia VRef: wartość znamionowa ± 20% | Częstotliwość pracy f: wartość znamionowa ± 20% | |

| Temperatura przechowywania Tstg: -65~150℃ | Zalecane warunki pracy | ||

| Logiczne napięcie zasilania VL: 5±0,5 V | Napięcie zasilania Vs: 15±0,75V | ||

| Napięcie sygnału V1: wartość znamionowa ±10% | Napięcie odniesienia VRef: wartość znamionowa ± 20% | Częstotliwość pracy f: wartość znamionowa ± 20% | — |

| Zakres temperatury roboczej (TA): -55℃~125℃ | Uwaga: * oznacza, że można go dostosować zgodnie z wymaganiami użytkownika. | Tabela 2 „Charakterystyka elektryczna” | Parametr |

| Warunki | — | Seria HSDC14569 | (VSu003d15V, VLu003d+5V) |

| Norma wojskowa (Q/HW20725-2006) | — | 2V | Min. |

| Maks. | — | Rezolucja | Równoległy kod cyfrowy systemu binarnego |

| 16 bitów | — | 2V | Dokładność |

| ± 10% napięcia sygnału, napięcia odniesienia i zakresu wahań częstotliwości roboczej | — | -2 minuty kątowe | +2 minuty kątowe |

| Zakres częstotliwości odniesienia | — | 50Hz | 2600 Hz |

| Zakres napięcia odniesienia | — | 115V | Referencyjna impedancja wejściowa |

4,4kΩ 4,4kΩ | — | 0 | 129,2 kΩ |

Zakres napięcia sygnału Zakres napięcia sygnału | — | 0 | 90V |

Impedancja wejściowa sygnału Impedancja wejściowa sygnału | — | 0 | 4,4kΩ |

| 102,2 kΩ | — | Przesunięcie fazowe sygnału/odniesienia | —70° |

| +70° | — | Poziom logiki wejściowej | Logika „1” ≥3,3 V |

| Logika „0” ≤0,8 V | — | Wejście | 0,8V |

| Wejście | — | 0,8V | |

| Wejście | — | — | 0,8V |

| Wyjściowy poziom logiki | — | — | Logika „1” ≥3,3 V |

| Logika „0” ≤0,8 V | — | — | Wyjście cyfrowego kodu kąta |

| Logika „1” ≥3,3 V | — | — | Logika „0” ≤0,8 V |

| Konwertowanie wyjścia sygnału zajętości (CB) | — | 200ns | 600ns |

| Wykrywanie błędów Wyjście bitowe | Logika „0” wskazuje błąd | — | Ładowność |

| 3TTL | Szybkość śledzenia | ||

| 2,5 obr./s | Stałe przyspieszenia | ||

| +10V Aktualny VSu003d+15V 10mA |  VS u003d-15V |

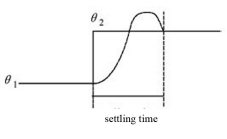

prędkość. Proces oscylacji wyjściowego kąta cyfrowego pokazano na:

prędkość. Proces oscylacji wyjściowego kąta cyfrowego pokazano na: 6. Zasada działania (rys. 3)

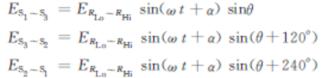

6. Zasada działania (rys. 3)| Przetworniki synchroniczne na cyfrowe lub konwertery resolwerowe na cyfrowe (seria HSDC/HRDC1459) Sygnał wejściowy synchronizacji (lub resolwera) jest konwertowany na sygnał ortogonalny przez wewnętrzną izolację różnicową: | |

Vcosu003dKE0sin (ωt+α) cosθ (cos)ofGdzie θ to kąt wejścia analogowego. Rys. 2 Krzywa odpowiedzi krokowej | Te dwa sygnały i kąt cyfrowy φ wewnętrznego licznika odwracalnegoof są mnożone przez mnożnik funkcji sinus i cosinus i są naprawiony błąd: |

| wzmocnienie, dyskryminacja faz i filtracja integracyjna, jeśli | θ-φ≠0, oscylator sterowany napięciem wygeneruje impulsy, a | licznik odwracalny zlicza, aż θ-φ osiągnie zero z dokładnością do | konwerter, podczas tego procesu konwersja śledzi zmianę | kąt wejściowy przez cały czas. | Metoda czytania: |

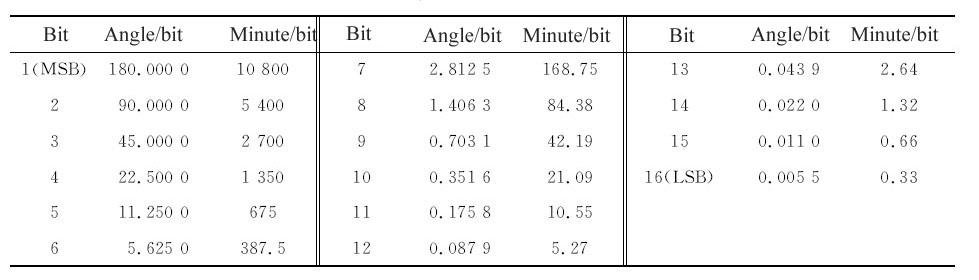

| 1 | S1 | Dostępne są dwie metody przesyłania danych: | 25 |  | (1) Metoda hamowania: |

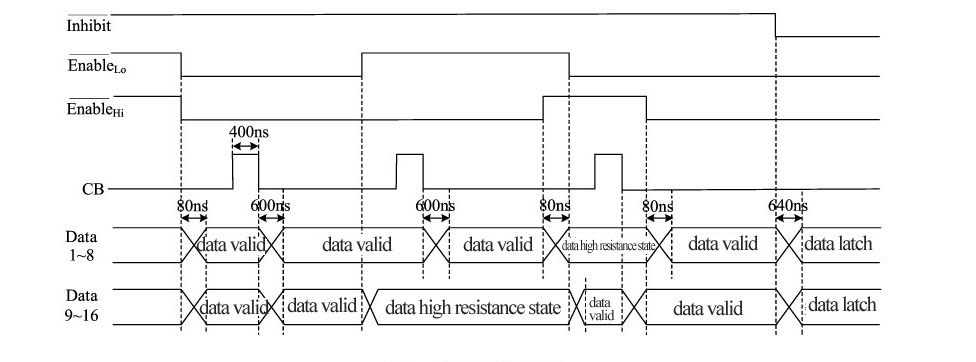

| 2 | S2 | Po 640 ns | 26 |  | stan logiczny niski, dane wyjściowe są prawidłowe, a konwerter realizuje transmisję danych przez |

| 3 | S3 | oraz | 27 | . Po zwolnieniu Inhibit system automatycznie wygeneruje impuls o szerokości równej impulsowi zajętości w celu aktualizacji danych. | (2) Tryb biustu: |

| 4 | S4 | Na rosnącej krawędzi impulsu zajętości zliczany jest trójstanowy licznik odwracalny; na opadającej krawędzi impulsu zajętości, wewnętrznie generuje impuls zatrzasku o szerokości równej impulsowi zajętości, w celu aktualizacji danych zatrzasku w trzech stanach, n.p. niskiego poziomu logiki zajętości, stabilny transfer danych jest prawidłowy. W trybie odczytu asynchronicznego wyjście Zajęty to ciąg impulsów na poziomie CMOS. Szerokość jego wysokiego i niskiego poziomu zależy od częstotliwości pracy i prędkości obrotowej wybranego urządzenia. | 28 | VL | Rys.4 Sekwencja czasowa przesyłania danych |

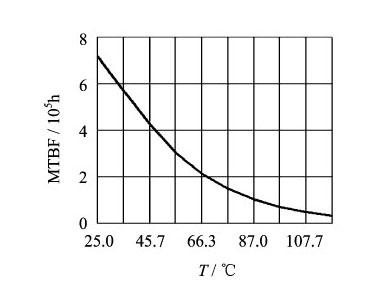

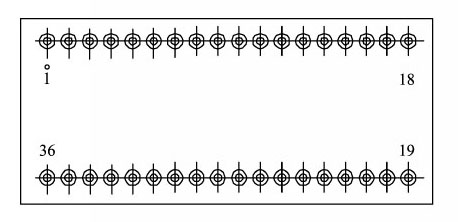

| 7. Krzywa MTBF (ryc. 5) | Przetworniki synchroniczne na cyfrowe lub konwertery resolwerowe na cyfrowe (seria HSDC/HRDC1459) | Rys.5 Krzywa temperatury MTBF | 29 | 8. Oznaczenie pinów (rys. 6, tabela 3) | Przetworniki synchroniczne na cyfrowe lub konwertery resolwerowe na cyfrowe (seria HSDC/HRDC1459) |

| 19 | Rys. 6 Oznaczenie styków (widok od dołu) | (Uwaga: zgodnie z GJB/Z299B-98, przewidywany dobry stan gruntu) | 30 | NC | Tabela 3 „Oznaczenie pinów” |

| 20 | RL | Szpilka | 31 | Symbol | Oznaczający |

| 21 | Szpilka | Symbol | 32 | VS | Oznaczający |

| 22 | Wejście resolwera S1 (lub wejście synchroniczne S1) | Włączona cyfrowa kontrola niższych 8 bitów | 33 | Wejście resolwera S2 (lub wejście synchroniczne S2) | Włączona cyfrowa kontrola wyższych 8 bitów |

| 23 | Wejście resolwera S3 (lub wejście synchroniczne S3) | RIPCLK | 34 | Zerobitowy sygnał wyjściowy | Wejście resolwera S4 (pozostaw niepodłączone) |

| 24 | CB | Zasilanie +5 V | 5月18日 | NC | D1-D14 |

| Wyjście cyfrowe 1 (MSB)-14 | GND |

| Grunt | RHi |

| Wysoki koniec wejściowego sygnału odniesienia | Brak połączenia |

| RL | Dolny koniec wejściowego sygnału odniesienia |

-VS

-VS Zasilanie -15 V

Zasilanie -15 V

D15 Wyjście cyfrowe 15

Wyjście cyfrowe 15 ).

).

Zasilanie +15 V

D16

Wyjście cyfrowe 16 (LSB)

Hamować

Wejście sygnału statycznego

Vel

S1, S2, S3, S4

S1, S2, S3, S4

Dolny koniec wejściowego sygnału odniesieniaofNiżej | 8-bitowe wejście sygnałowe z obsługą cyfr, ten pin jest pinem wejścia logicznegoofkontrola bramkowania danych, jej funkcją jest realizacja kontroli trójstanowej |

|  |

| zewnętrznie na niższych 8-bitowych danych wyjściowych konwertera. Niski poziom to | prawidłowe, niższe 8-bitowe dane wyjściowe konwertera zajmują dane |

stan rezystancji, a urządzenie nie zajmuje magistrali danych. Włączyća czas opóźnienia zwolnienia wynosi 600ns (maks.). | wyższy | 8-bitowe wejście sygnałowe z obsługą cyfr, ten pin jest pinem wejścia logicznego | kontrola bramkowania danych, jej funkcją jest realizacja kontroli trójstanowej | zewnętrznie na wyższych 8-bitowych danych wyjściowych konwertera. Niski poziom | jest prawidłowy, wyższe 8-bitowe dane wyjściowe konwertera zajmująmagistrala danych; Na wysokim poziomie pin wyższych 8-bitowych danych wyjściowych jest wysoki | stan rezystancji, a urządzenie nie zajmuje magistrali danych. Włączyć | a czas opóźnienia zwolnienia wynosi 600ns (maks.). | Zablokuj statyczne |

wejście sygnału, ten pin jest pinem wejściowym logiki sterującej, jego funkcją; | jest wyprowadzanie danych zewnętrznie do konwertera w celu realizacji opcjonalnej; | Nisterowanie zatrzaskiem lub obejściem. Na wysokim poziomie dane wyjściowe | konwerter bezpośrednio wyjścia bez zatrzasku; na niskim poziomie wyjście | dane konwertera są zatrzaśnięte, dane nie są aktualizowane, alepętla wewnętrzna nie jest przerywana, a śledzenie działa przez cały czas | czas, Inhibit połączył wewnętrznie opór podciągania. Po 600ns (maks.) opóźnienie | Au opadająca krawędź sygnału statycznego, dane stają się stabilne (czy | urządzenie zajmuje magistralę danych, tj. kiedy wyprowadza dane, zależy od tego, kiedyo stanie | orazWyjście sygnału CB „Zajęty”, ten sygnał wskazuje, czy kod binarny |

X

X